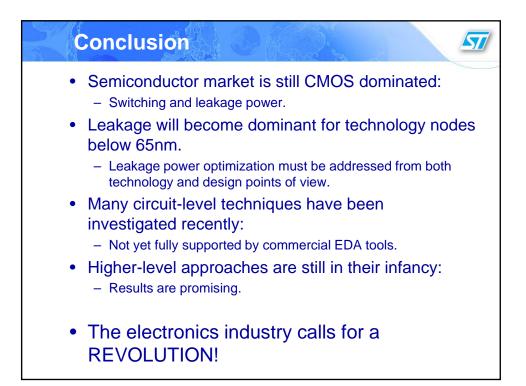

| "Leakage Aware" design strategy includes |                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

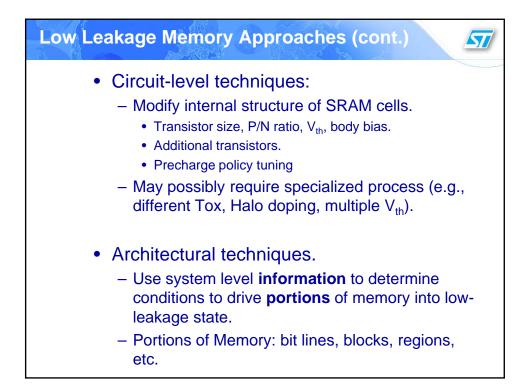

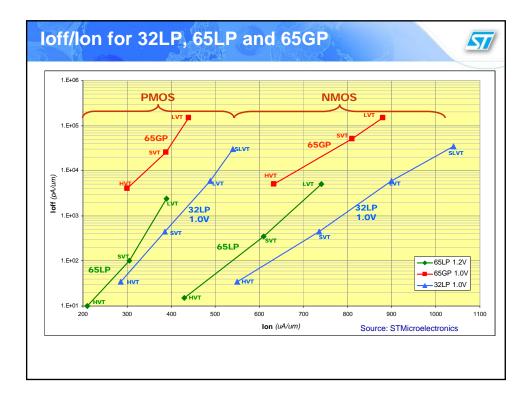

| A.                                       | Gate/Circuit-level techniques<br>Use of multiple V <sub>th</sub><br>• Dual-V <sub>th</sub> design.<br>• Mixed-V <sub>th</sub> (MVT) CMOS design.<br>• MTCMOS.<br>- Sleep transistor insertion/Voltage islands<br>- State retention FFs                                                                                                                               |

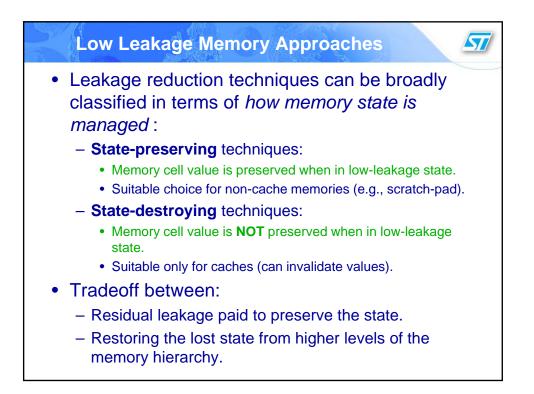

| В.                                       | <ul> <li>Techniques for memory circuits</li> <li>Cell state (stored value) determines exactly which transistors "leak"</li> <li>State-preserving techniques: <ul> <li>Only suitable choice for non-cache memories (e.g., scratchpad).</li> </ul> </li> <li>State-destroying techniques: <ul> <li>Suitable for caches (can invalidate values).</li> </ul> </li> </ul> |

| C.                                       | <ul> <li>Architectural techniques</li> <li>Adaptive Body Biasing (ABB).</li> <li>Adaptive Voltage Scaling (AVS).</li> <li>V<sub>th</sub> hopping.</li> <li>Multiple V<sub>BB</sub></li> </ul>                                                                                                                                                                        |