# Computer Science

Acknowledgement: Sun Microsystems, CNS, NSF GreenLight, UC Micro, Cisco, GSRC, DARPA

# THERMAL MANAGEMENT IN HETEROGENEOUS MULTIPROCESSOR SOCS

Shervin Sharifi Ayse K. Coskun

A. Voltage/Frequency Configuration Calculation

Tajana Rosing

Computer Science and Engineering Department, University of California San Diego (UCSD)

# THERMAL CHALLENGES

#### Thermal Hot Spots

- High leakage power

- Slower devices

- Degraded reliabilityHigher interconnect

- resistivity Thermal Cycles

- Higher permanent failure rate

- Spatial Gradients

- Timing failuresIncreased interconnect

- delay and IR drop

# ect vaccosi a generation a second

# HETEROGENEOUS MPSoCs

#### MPSoCs vs. Single core CPUs

- Higher performance per Watt

- Lower design complexity

- Heterogeneous MPSoCs

- Integrate cores with different architectures &

- various power/performance characteristics • Allow customized power/performance for the

- current requirements of application

#### Challenges

- Efficient tuning of power/performance under thermal constraints

- Large thermal variations due to inherent disparities in power densities across the chip

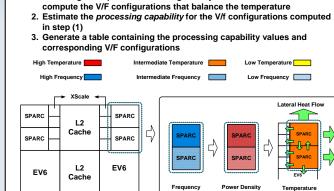

## FLOW

- Offline Phase → Performed once at design time

- Calculates voltage/frequency configurations for thermal balancing

- Characterizes tasks to pick the preferred core for each task

Online Phase → Performed repeated/v at runtime

- One of the V/F configurations calculated in offline phase is selected to meet the current performance demand

- Tasks are balanced among cores to maximize the performance under the current V/F setting

Task Assignment

**OFFLINE PHASE**

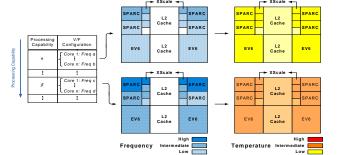

1. For a target temperature and the given layout and core characteristics

#### **B. Task Characterization**

Benchmarks from the MiBench suite :

в

Thermal Simulator:

Workloads:

Benchmark mixes:

Contains equal number

in-tolerant benchmarks

of frequency tolerant and

Α

Automotive, networking and telecommunication

applications (fft, disjkstra, bitcount, patricia, etc.)

HotSpot [Skadron, ISCA'03] with a cheap package

A mix of the MiBench benchmarks [Guthaus et al. WWC'01]

running on small cores → "Frequency Tolerant Benchmarks"

С

D

benchmarks

Contains mostly

frequency tolerant

\* Some benchmarks have low performance penalty when

Determines which core type is the best fit to run a task on based on runtime changes when run on different cores

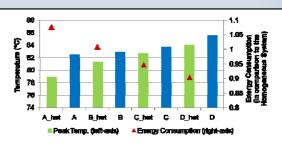

A, B, C, D: Workload running on a homogeneous MPSoC of **4 EV6 cores** \*\_het: Workload on a heterogeneous MPSoC of **2 EV6s, 4 SPARCs and 8 XScales**

## **ONLINE PHASE**

#### 1. Voltage/Frequency Selection

- Processing demand is calculated based on the task arrival rates and lengths

The lowest processing capability which meets the current demand is selected

- from the table generated in offline phase (A)

The corresponding V/F configuration is assigned to the MPSoC

#### 2. Task assignment

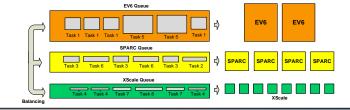

Each core type (e.g. EV6, SPARC, Xscale) has a corresponding queue

- Tasks suitable for a certain type of core are directed to the appropriate queue

- · Tasks are moved among queues if there is imbalance

## EXPERIMENTAL RESULTS

On a heterogeneous MPSoC of EV6, SPARC and XScale cores, our thermal management technique achieves: • Up to 10% additional energy savings • Up to 4°C decrease in peak temperature •Spatial gradients lower than 5°C in comparison to a homogeneous EV6based MPSoC with the same die area, while maintaining the performance constraints.